La batalla por el dominio en transistores CFET de apilamiento vertical: Intel vs TSMC, ¿quién triunfará en innovación?

Aunque los transistores GAA aún no han llegado al mercado, ya se habla de los CFET, y tanto TSMC como Samsung están enfrentando dificultades en la producción. Intel parece estar avanzado en este aspecto, con la introducción de su primer nodo Intel 20A el próximo año. En diciembre, Intel y TSMC discutirán sus avances en el International Electron Devices Meeting (IEDM), y ya han presentado algunos planes preliminares. La pregunta es cuál de las dos empresas tiene un diseño más avanzado para los transistores CFET.

El apilamiento vertical se ha aplicado a los transistores después de las CPU y GPU, y los transistores CFET tienen un diseño muy intrincado. El IEDM será un punto de partida para los diseños CFET, liderado por Intel y TSMC. Hasta ahora, Samsung no ha revelado sus planes, y es posible que no lo hagan hasta el evento.

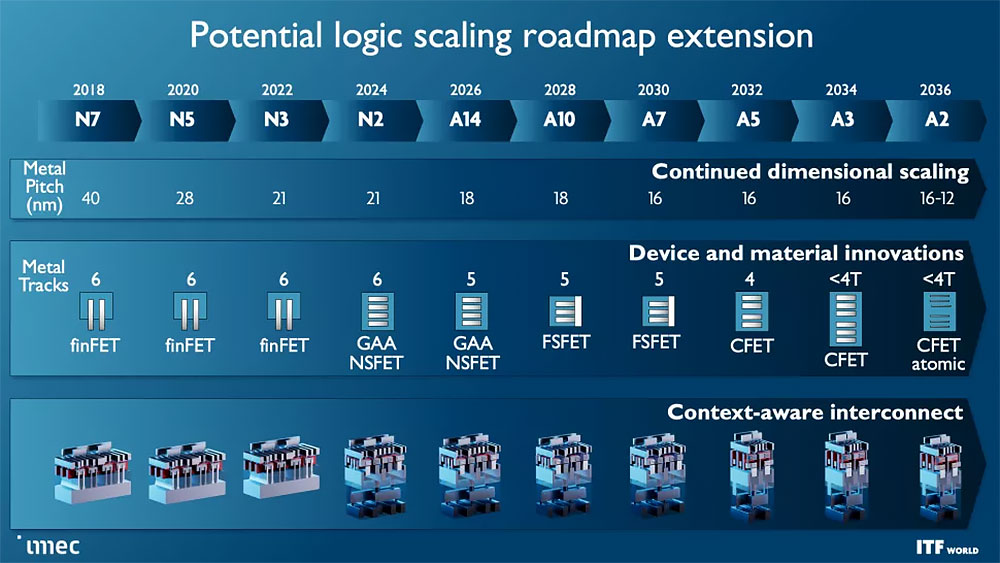

Los transistores Complementary FET (CFET) son una arquitectura que apila dispositivos nMOS y pMOS verticalmente, permitiendo una mayor optimización y maximización del ancho efectivo del canal de conexión. Esta tecnología representa dos pasos adelante de los actuales GAA, con el Forksheet en medio, un desarrollo del GAA donde las nanosheets se agrupan en ambos lados del Metal Gate.

Se habla de CFET en el IEDM debido a la complejidad que requiere mucha investigación, ensayo y error. Intel y TSMC han enviado sus propuestas preliminares al simposio, proporcionando algunos detalles.

El enfoque de Intel es un transistor CFET 3D monolítico simétrico, con tres nanosheets nMOS apiladas sobre tres nanosheets pMOS y una separación vertical de solo 30 nm. Mostrarán y describirán “fully functioning inverter test circuits in CFET” con un Gate Pitch de 60 nm y Dual Metal Work function Gate Stacks, incluyendo el sistema BSPD patentado de Intel, conocido como PowerVia.

TSMC sigue un camino similar al de Intel, anunciando un diseño de transistores CFET con un Gate Pitch de 48 nm. Han logrado no solo una reducción del espacio final de cada transistor, sino también una relación entre la corriente de encendido y apagado de seis órdenes de magnitud. Además, TSMC afirmó que demostraron una durabilidad con una tasa de éxito de más del 90%.

Ambas empresas están trabajando en la densidad, eficiencia y control energético de los transistores, un cambio significativo desde FinFET. Veremos en diciembre quién lleva la ventaja en el diseño de los transistores CFET, Intel o TSMC.

Contact Comprar Magazine.

Consultas al por mayor solamente.

Email: eblast@comprarmag.com

Tel: | Whatsapp:

Leave a Reply

Want to join the discussion?Feel free to contribute!