Primeros prototipos revelados: Intel, Samsung y TSMC desvelan transistores CFET revolucionarios para los chips del futuro

Hace unos meses, comenzamos a hablar acerca del futuro de los chips, ya que GAA (Nanosheet) es una realidad en Samsung, pronto lo será en Intel y se retrasará notablemente en TSMC. Por lo tanto, y considerándolo como el presente, el siguiente paso en los transistores y su organización es CFET, antes de llegar a la segunda generación de GAA llamada Forksheet. Dado que aún hay mucho tiempo por delante y que el avance es complicado, Intel, Samsung y TSMC han presentado los primeros prototipos de CFET durante la IEEE International Electron Devices Meeting, revelando sus distintos enfoques. ¿Quién tiene el mejor diseño preliminar?

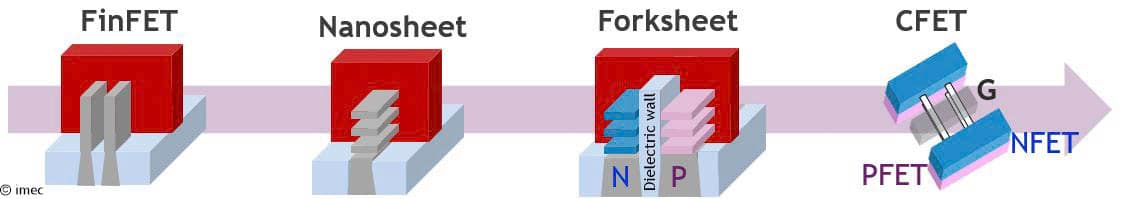

Los distintos tipos de transistores han evolucionado desde FinFET y sus variantes hasta GAA y sus respectivas versiones, y se espera que en unos años se den paso a las posteriores versiones de CFET. Como ya sabemos, GAA ha traído al mercado las Nanosheets como dos partes dentro de un transistor, que desde la perspectiva tradicional, son en realidad dos transistores. Aunque puede resultar difícil de comprender, aquí presentaremos una simplificación y luego profundizaremos en el tema.

En FinFET, había una sola compuerta vertical (Gate) donde se controlaba la corriente y su flujo mediante una aleta (Fin). Con GAA, todo se vuelve más complejo ya que esa aleta se ha dividido en varios Fins verticales, que además tienen más área de contacto con la compuerta.

El siguiente paso, como mencionamos antes, es Forksheet, el cual agrega más complejidad como la segunda generación (evolución, según algunos ingenieros) de GAA, ya que las Nanosheets verticales se dividen en dos tipos, nFET y pFET, que ahora están conectadas a una pared dieléctrica que, dependiendo del diseño, cumple con la función de inversor.

Después de esto, y ya en la próxima década, aparece el mencionado CFET, el cual divide completamente los nFET y pFET. La forma en que se interpreta este hecho es lo que vamos a conocer por primera vez hoy. ¿Cómo han diseñado Intel, TSMC y Samsung su interpretación de CFET?

Intel ha diseñado un inversor para sus transistores CFET y lo presentó en el IEEE. El diseño aún tiene muchos detalles por revelar, pero sí se han compartido los aspectos más importantes. Los bocetos preliminares de TSMC y Samsung mostraron que estos diseños serían laterales, es decir, la disposición entre nFET y pFET sería horizontal al estar divididos ahora. Sin embargo, Intel toma un enfoque diferente, con un diseño de apilamiento vertical 3D. Esto presenta el desafío de cómo conectar verticalmente nFET y pFET y cómo suministrar energía a ambos estando separados verticalmente. La solución de Intel es un inversor, un circuito simple de conexión para obleas de silicio que está unido a Power Via, o sea, a la tecnología BSPDN de Intel (en su interpretación, para ser más precisos).

Marko Radosavljevic, ingeniero principal de Intel en transistores, lo explica de la siguiente manera:

“Usamos PowerVia para conectar el dispositivo superior a la parte posterior de la oblea y usamos los contactos directos de la parte posterior para conectar el dispositivo inferior. Dado que estos dispositivos están apilados uno encima del otro, no existe una forma directa de conectar el dispositivo inferior al lado superior de la oblea, por lo que tenemos que hacerlo como se acaba de describir”.

Intel ha compartido más información, llamando a los nFET y pFET como N-EPI y P-EPI. Este sistema tiene dos ventajas claras y una desventaja. Comenzando por lo negativo, es realmente complejo de diseñar y lograr. Sin embargo, por otro lado, el sistema de inversor CMOS diseñado envía el mismo voltaje de entrada a ambas compuertas para nFET y pFET, lo que significa que la salida es lógicamente la inversa de dicha entrada para ambos.

La segunda ventaja es que, al lograr esto, se consigue el mencionado apilamiento vertical y esto mejora el área total, lo que debería llevar a una mayor densidad en MTr/mm2. Sin embargo, esto solo se logrará si Intel consigue compactar cada transistor verticalmente manteniendo lo dicho anteriormente.

En cuanto a TSMC, la compañía afirma que su CPP es mejor que el de Intel, alcanzando 48 nm, lo que iguala sus cifras en el nodo N3 actual. Por otro lado, Samsung, que fue pionero en GAA al dejar los diseños FinFET antes que nadie, presentó un CPP de entre 48 nm y 45 nm en el IEEE, mucho mejor que el de Intel. Sin embargo, estas cifras son para nFET y pFET individuales, no conectados horizontalmente entre Nanosheets. Tampoco hay datos sobre un posible inversor y su CPP.

Dadas las presentaciones de los tres diseños y sus primeros bocetos reales, es importante entender que aún estamos a 6 o 7 años de que lleguen al mercado, por lo que aún hay tiempo para que Intel, TSMC y Samsung continúen desarrollando estos nuevos tipos de transistores CFET, que sin duda representan una nueva revolución para los futuros chips.

Contact Comprar Magazine.

Consultas al por mayor solamente.

Email: eblast@comprarmag.com

Tel: | Whatsapp:

Leave a Reply

Want to join the discussion?Feel free to contribute!